# Optically functional surface composed of patterned graded-refractive-index coatings to enhance light-extraction of GalnN light-emitting diodes

Ahmed N. Noemaun, <sup>1,a)</sup> Frank W. Mont, <sup>1</sup> Guan-Bo Lin, <sup>1</sup> Jaehee Cho, <sup>1</sup> E. Fred Schubert, <sup>1</sup> Gi Bum Kim, <sup>2</sup> Cheolsoo Sone, <sup>2</sup> and Jong Kyu Kim<sup>3</sup>

(Received 13 June 2011; accepted 31 July 2011; published online 9 September 2011)

Graded-refractive-index (GRIN) coatings, composed of multiple dielectric layers of TiO<sub>2</sub> and SiO<sub>2</sub> are sputter-deposited on the nitrogen-face of thin-film GaInN/GaN light emitting diodes (LEDs). The thickness and refractive index of each layer in the GRIN stack is designed to minimize light trapping inside the LED caused by total internal reflection at the semiconductor–air interface. Patterning the GRIN stack forms an optically functional surface, which converts trapped modes of light into desirable extracted modes that have preferential directions. Inductively coupled-plasma reactive-ion-etching is used to fabricate various patterns, including arrays of cylindrical pillars and diamond-shaped pillars on the GRIN coatings. In comparison to an uncoated planar reference device, the light-output power is enhanced by 131% and 104% for an array of GRIN diamond-shaped pillars and an array of GRIN cylindrical pillars, respectively. This enhancement in light-output power is comparable to N-face roughened LEDs, which show an enhancement of 124%. In addition, the peak emission intensity of the GRIN LEDs with an array of GRIN pillars is between 25° and 55° off-surface-normal. © 2011 American Institute of Physics. [doi:10.1063/1.3632072]

#### I. INTRODUCTION

Total internal reflection (TIR), caused by the high refractive index contrast between the semiconductor of light emitting diodes (LEDs) and the surrounding medium, traps light as guided modes inside the semiconductor. This leads to a significant portion of the light, generated by the active region of the LED, remaining confined inside the semiconductor material. Only a small percentage of light ( $\approx 1/4n^2$  per surface, where n is the high refractive index of the semiconductor) is extracted from the LED chip when no techniques promoting light-extraction are used. Various efforts to address this fundamental problem include wet-chemical texturing of the LED chip surface, 2-7 2D photonic crystals, 8,9 planar graded-refractive-index anti-reflection coatings, 10 patterning of sapphire substrates, 11 and the shaping of LED chips. 12 The fabrication of sub-micron patterns by lithography is elaborate and limits the application of photonic crystals for LEDs. Crystallographic wet chemical texturing is the most popular technique to enhance light extraction of GaInN LEDs, but can be applied only to thin-film LEDs with the nitrogen-face (N-face) GaN surface being exposed. Also, epitaxial growth of a relatively thick GaN layer is required for KOH based wet chemical etching. Due to the crystalplane dependent etch rate, the surface roughness is highly random and results in a Lambertian emission pattern. In comparison, non-random features of graded-refractive-index (GRIN) patterns can be designed and deliberately fabricated on the surface of an LED chip. The GRIN patterns make the

surface of the chip optically functional, i.e., when properly designed, the emission direction can be tailored, increasing the light emission in desired directions and thus eliminating the use of lossy secondary and tertiary optics on the LEDs.

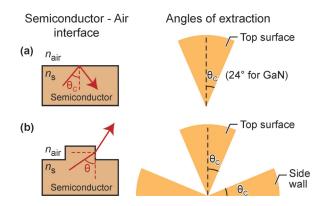

# II. THEORETICAL CALCULATION AND DESIGN OF GRIN PATTERNS

The structure of a standard LED is a rectangular parallelepiped with six planar surfaces. Each of these surfaces can be a semiconductor-air/epoxy interface with high refractive index contrast. As shown in Fig. 1(a), only those light rays striking the interface at an angle less than the critical angle,  $\theta_{\rm c} = \sin^{-1}(n_0/n_{\rm s})$ , can be transmitted to the surrounding medium. Thus, transmittance of light through a planar surface is restricted to an escape cone, which is bounded by the critical angle. When a GaN LED, with emitting wavelength of 450 nm and refractive index  $n_s = 2.47$  is surrounded by air,  $n_0 = 1$ , the critical angle at the interface is only 24°. All rays of light incident at the surface between 24° and 90° are totally internally reflected back into the semiconductor. Assuming isotropic emission inside the GaN LED and using a high-refractive-index approximation, only about  $n_0^2/4n_s^2$  $\approx 4\%$  is extracted through each surface.<sup>1</sup>

For the sake of simplicity, a planar geometry is considered to trace the path of light rays striking the semiconductorair interface. In case of a cylindrical pillar of refractive index  $n_{\rm p}$  being formed on a semiconductor surface, as shown in Fig. 1(b), light is extracted through the top surface of the pillar as well as the circular surface forming the side of the pillar, thus enhancing the total range of angles which are extracted from

<sup>&</sup>lt;sup>1</sup>Department of Electrical, Computer, and Systems Engineering, Rensselaer Polytechnic Institute, Troy, New York 12180, USA

<sup>&</sup>lt;sup>2</sup>R&D Institute, Samsung LED, Suwon 443-744, South Korea

<sup>&</sup>lt;sup>3</sup>Department of Materials Science and Engineering, Pohang University of Science and Technology, Pohang 790-784, Korea

<sup>&</sup>lt;sup>a)</sup>Electronic mail: ahmedn3@rpi.edu.

FIG. 1. (Color online) (a) For a planar semiconductor, only those light rays striking the interface at an angle less than the critical angle,  $\theta_{\rm c}$  (24° for GaN), are transmitted to the surrounding medium. (b) When a pillar is placed on the semiconductor, light can be extracted through the top surface of the pillar as well as the circular side surface of the pillar.

the semiconductor. If  $n_{\rm p} = n_{\rm s} = 2.47$  (for GaN), then light striking the semiconductor-pillar interface at angles between  $\theta = 66^{\circ}$  and  $\theta = 90^{\circ}$  could enter the pillar and then be extracted through the sidewall. The probability of a light ray to strike the sidewall after entering the pillar will depend on the height and diameter of the pillar.

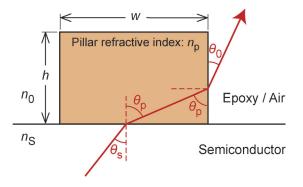

Fig. 2 shows a light ray that strikes the semiconductor–pillar interface at an incident angle  $\theta_{\rm s}$ , enters the cylindrical pillar at an angle  $\theta_{\rm p}$ , and leaves the cylindrical pillar at an angle  $\theta_{\rm 0}$ . For a ray to trace this path, the ray should not be total internally reflected at the semiconductor–pillar interface or the pillar–air interface. According to Snell's law, a lower and upper bound on the refractive index of the pillar,  $n_{\rm p}$ , avoids TIR at the semiconductor–pillar interface and pillar–air interface, respectively.

Lower Bound: For absence of TIR at the semiconductorpillar interface,

$$n_{\rm p} > n_{\rm s} \sin \theta_{\rm s}$$

. (1)

Upper Bound: For no TIR at the horizontal pillar-air interface,

$$n_0 > n_{\rm p} \sin(90^\circ - \theta_{\rm p}). \tag{2}$$

Also from the Snell's law at the semiconductor-pillar interface,

FIG. 2. (Color online) Light ray at an incident angle,  $\theta_s$ , strikes the pillar of refractive index,  $n_p$ , and height, h. The ray leaves the pillar at an angle  $\theta_0$ .

$$n_{\rm s}\sin\theta_{\rm s} = n_{\rm p}\sin\theta_{\rm p}.$$

(3)

By squaring Eqs. (2) and (3) and adding the LHS and RHS, we get

$$n_0^2 + n_s^2 \sin^2 \theta_s > n_p^2$$

. (4)

Rearranging Eq. (4) and taking the square root, we get

$$n_{\rm p} < \sqrt{n_0^2 + n_{\rm s}^2 \sin^2 \theta_{\rm s}}.$$

(5)

For each angle of incidence,  $\theta_s$ , of a ray striking the semiconductor–pillar interface, there is a lower and upper bound for the refractive index of the pillar,  $n_p$ , to avoid TIR, given by Eqs. (1) and (5), respectively. By using different refractive index layers stacked on top of each other, pertaining to a range of angles of incidence at the semiconductor–pillar interface, TIR for all angles above the critical angle can be completely eliminated. Also, the higher refractive index layers need to be stacked at the bottom of the pillar to avoid TIR between these layers.

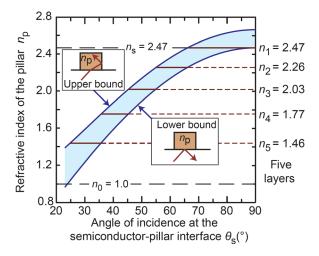

As shown in Fig. 3, for a GaN LED, the first layer of the pillar with refractive index  $n_{\rm p1} = 2.47$  extracts rays with  $90^{\circ} > \theta_{\rm s} > 66^{\circ}$ . The height of the first layer is chosen such that the ray incident on the semiconductor–pillar interface at  $66^{\circ}$  necessarily meets the sidewall of the first layer of the pillar. If  $h_1$  is the height of the first layer and w is the diameter of the pillar, the geometric condition that needs to be fulfilled is as follows:

$$h_1 > \frac{w \tan \theta_c}{2}$$

, where  $\theta_c = \sin^{-1} \left( \frac{n_0}{n_{p1}} \right)$ . (6)

The second layer of the pillar with refractive index  $n_{\rm p2} = 2.26$  extracts rays with  $66^{\circ} > \theta_{\rm s} > 55^{\circ}$ . The height of the second layer is chosen such that the ray incident on the semiconductor–pillar interface at  $55^{\circ}$  necessarily meets the sidewall of the second layer of the pillar. With 5 layers corresponding to 5 independent ranges of angles listed in Fig. 3, all rays of light incident on the semiconductor–pillar

FIG. 3. (Color online) Five discrete layers are designed, using the upper and lower bound of the refractive index, to extract all light incident on the semiconductor–pillar at angles greater than the critical angle,  $\theta_{\rm c}$  (24° for GaN).

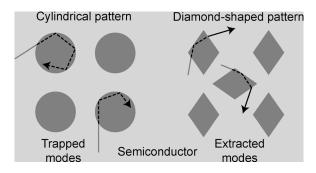

FIG. 4. Schematic showing the top view of cylindrical and diamond-shaped patterns placed on the top surface of the semiconductor. The transparent lines, dashed lines, and solid lines depict the light rays inside the semiconductor, inside the pillars, and extracted by the patterns, respectively.

interface at angles greater than the critical angle 24° can be extracted through the side walls of the different layers of the pillar. For certain spacing between the pillars, the height of each layer in the GRIN stack is a trade-off between (i) maximizing light emitted through the side walls and (ii) lowering the probability of light re-entering a neighboring pillar.

The GRIN patterns are designed to eliminate total internal reflection in the cross-sectional plane normal to the surface of the semiconductor. Light can continue to be trapped in the surface plane of the semiconductor. Few of the light rays inside cylindrical pillars reflect off the side walls and remain trapped. These trapped rays move along the periphery and are often referred to as whispering gallery modes. When the pattern contains pointed shapes, such as a diamondshape, the light ray reflects at the sharp edges and eventually escapes from the pillar. Fig. 4 depicts trapped modes inside the cylindrical pattern and the extracted modes in a diamond-shaped pattern. Diamond-shaped pillars, when placed complimentary to each other, presumably extract all trapped modes inside the semiconductor.

#### **III. FABRICATION PROCEDURE**

Thin-film vertical  $1 \times 1 \text{ mm}^2$  GaInN LEDs emitting at 445 nm are used as a reference. They are grown by metalorganic vapor-phase epitaxy on a c-plane sapphire substrate and consist of an undoped GaN buffer layer, an n-type GaN layer, a GaInN/GaN multiple quantum-well active region, a p-type AlGaN electron blocking layer, and a p-type GaN upper cladding layer. A KrF excimer laser is used for a laser lift-off process to separate the GaN from the sapphire substrate. For the planar reference LEDs, the separated N-face GaN surface is planar and has no passivation layer. The roughened reference LEDs have N-face GaN surface roughened by crystallographically wet etching using an aqueous 10% KOH (weight ratio) solution for 4 min at 50 °C.

GRIN patterns are fabricated on the N-face of LEDs with identical epi-structure as follows: Varying compositions of TiO<sub>2</sub> and SiO<sub>2</sub> are sputter-deposited on the N-face of thin film LEDs. Argon and oxygen gases are flown into the sputter chamber at flow rates of 10 sccm and 0.5 sccm, respectively. The pressure of the chamber is maintained at 2 mTorr. The substrate plasma is generated at 100 V bias and the substrate is kept at room temperature during the sputter deposition. Each  $(TiO_2)_x(SiO_2)_{1-x}$  layer has a desired x value, which is achieved by adjusting the electrical power applied to the two sputtering targets. Ellipsometry measurements are used to determine the refractive index and thickness of the thin films deposited on the substrates. The refractive index of each  $(TiO_2)_x(SiO_2)_{1-x}$  layer depends on the volume ratio of the TiO<sub>2</sub> and SiO<sub>2</sub> mixture. Table I shows the power applied to the TiO<sub>2</sub> and SiO<sub>2</sub> targets, the duration of the sputterdeposition, the measured refractive index, and the measured thickness of the five layers of TiO2 and SiO2 that are deposited to form the GRIN stack. The total thickness of the GRIN stack is around 1.6  $\mu$ m. Additionally, 127 nm of ITO is sputter-deposited to serve as a hard mask for the following inductively coupled plasma (ICP) reactive ion etch (RIE).

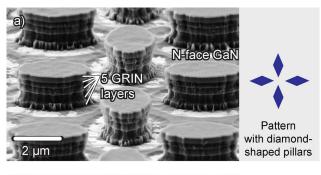

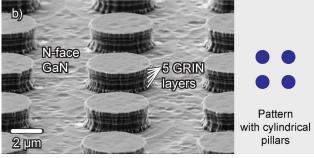

Photo-lithography for patterning the ITO hard mask is performed with Shipley Company's S1813: a standard photoresist. Various patterns are formed on the ITO layer, including arrays of cylindrical pillars with diameter 2  $\mu$ m and spacing 2  $\mu$ m and diamond-shaped pillars with a longer diagonal of 4.7  $\mu$ m and a shorter diagonal of 2  $\mu$ m. The ITO layer is etched under 200 W ICP power and 150 W RIE power with 10 sccm of CH<sub>4</sub>, 100 sccm of H<sub>2</sub>, and 10 sccm of Cl<sub>2</sub> at 10 mTorr and 50 °C for 300 s to form the ITO hard mask. The GRIN coatings are subsequently etched under 1000 W ICP power and 400 W RIE power with 60 sccm of CHF<sub>3</sub> at 15 mTorr and 50 °C for 160 s. The remaining plasma etch residue along the side walls is removed by dipping the LEDs in AZ 300t (photoresist stripper) at 80 °C for 30 min. Figs. 5(a) and 5(b) show SEM images of an array of GRIN diamond-shaped pillars and an array of cylindrical pillars, respectively, on the N-face GaN thin-film vertical LEDs. The sidewall is near vertical with a tilt angle of less than  $5^{\circ}$ , and the remaining residue is minimal.

### IV. EXPERIMENTAL RESULTS AND DISCUSSION

At an injection current of 4 mA, the forward voltage is around 2.64 V for the planar reference LEDs, 2.7 V for the roughened LEDs, and 2.67 V for the LEDs with GRIN

TABLE I. Thickness and refractive index of each layer in the graded-refractive-index stack is controlled by the power applied to the TiO2 and SiO2 targets and the deposition time.

| Layer number | Power applied to TiO <sub>2</sub> target | Power applied to SiO <sub>2</sub> target | Deposition time | Measured layer thickness | Measured refractive index |

|--------------|------------------------------------------|------------------------------------------|-----------------|--------------------------|---------------------------|

| 1            | 200 W                                    | 0 W                                      | 240 min         | 333 nm                   | 2.47                      |

| 2            | 200 W                                    | 50 W                                     | 180 min         | 331 nm                   | 2.26                      |

| 3            | 200 W                                    | 100 W                                    | 120 min         | 323 nm                   | 1.99                      |

| 4            | 200 W                                    | 150 W                                    | 90 min          | 330 nm                   | 1.83                      |

| 5            | 0 W                                      | 200 W                                    | 120 min         | 260 nm                   | 1.46                      |

FIG. 5. (Color online) SEM images of (a) an array of diamond-shaped pillars and (b) an array of cylindrical pillars etched under 1 kW ICP power and 400 W RIE power with 60 sccm of  $CHF_3$  at 15 mTorr and 50 °C.

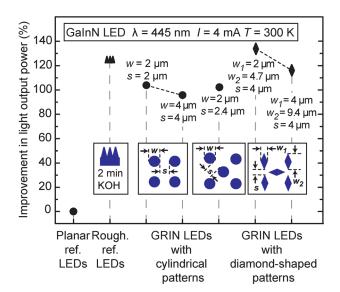

patterns. The light-output power from the LED chip is measured using a lab-made far-field emission setup with a blue-enhanced Si PIN photo-detector that is moved by a rotating arm similar to goniometry. The alignment of samples and non-interference of the probe tips with the measurement are important for a symmetric far-field measurement. The total light-output power is calculated by integrating the voltage measured on a resistive load of the photo-detector at various emission angles. Fig. 6 shows the improvement in total light-output power for the planar reference LEDs, the roughened reference LEDs, and the GRIN LEDs with cylindrical and diamond-shaped patterns. The total light-output power of roughened reference LEDs is enhanced by 124% in compari-

FIG. 6. (Color online) Light-output power of planar reference LEDs, roughened reference LEDs, LEDs with GRIN cylindrical patterns, and LEDs with diamond-shaped patterns.

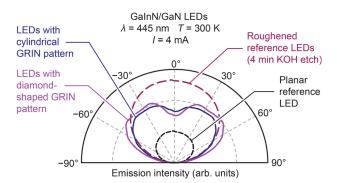

FIG. 7. (Color online) Far-field emission intensity of planar reference LEDs, KOH-roughened reference LEDs, LEDs with GRIN cylindrical patterns with 2  $\mu$ m diameter, and LEDs with GRIN diamond-shaped patterns with 4.7  $\mu$ m longer diagonal and 2  $\mu$ m shorter diagonal.

son to the planar reference LED. The total light-output power is enhanced by 131% and 104% with an array of GRIN diamond-shaped pillars with 4.7  $\mu$ m longer diagonal (and 2  $\mu$ m shorter diagonal) and with an array of GRIN cylindrical pillars with 2  $\mu$ m diameter, respectively. Also, the total light-output power is less for larger width and diameter of the same pattern. Fig. 7 shows far-field emission intensity of the planar reference LEDs, the roughened LEDs, and the GRIN-patterned LEDs. The maximum intensity of light is at 0° (normal to the surface of the LED) and the far-field pattern is Lambertian for both the planar reference and the roughened LED. However, the peak emission intensity of the LED with GRIN pillars is between 25° and 55° off-surface-normal. The strong side emission is consistent with our expectations resulting from theoretical calculations.

#### V. SUMMARY

We have proposed and demonstrated a strategy to design graded-refractive-index patterns that enhance the light extraction of LEDs. GRIN coatings made up of multiple dielectric layers of TiO<sub>2</sub> and SiO<sub>2</sub> are patterned to form pillars by ICP-RIE using the ITO hard mask. In comparison to the planar reference device, the total light-output power is enhanced by 131% and 104% with an array of GRIN diamond-shaped pillars with 4.7  $\mu$ m longer diagonal (and 2  $\mu$ m shorter diagonal) and with an array of GRIN cylindrical pillars with 2  $\mu$ m diameter, respectively. In addition, the peak emission intensity of the LED with an array of GRIN pillars is between 25° and 55° off-surface-normal. The patterned GRIN coatings are a novel type of optically functional surface which can convert trapped modes of light inside a semiconductor into designable modes with desirable properties, such as preferential direction of emission and polarization of light.

## **ACKNOWLEDGMENTS**

The authors gratefully acknowledge support from Samsung LED Co., Korean Ministry of Knowledge Economy through International Collaborative R&D Program, Sandia National Laboratories, National Science Foundation, Department of Energy, Department of Defense, NY State Energy Research and Development Authority, Magnolia Solar Inc., and Raydex Technology, Inc. The RPI authors also

054510-5

acknowledge the expert technical assistance from Bryant Colwill and Kent Way at the Micro and Nano fabrication clean room in Rensselaer Polytechnic Institute.

- <sup>1</sup>E. F. Schubert, Light Emitting Diodes, 2nd ed. (Cambridge University Press, Cambridge, 2006).

- <sup>2</sup>T. Fujii, Y. Gao, R. Sharma, E. L. Hu, S. P. Denbaars, and S. Nakamura, Appl. Phys. Lett. 84, 855 (2004).

- <sup>3</sup>Y. Gao, T. Fujii, R. Sharma, K. Fujito, S. P. Denbaars, S. Nakamura, and E. L. Hu, Jpn. J. Appl. Phys. 43, L637 (2004).

- <sup>4</sup>O. B. Shchekin, J. E. Epler, T. A. Trottier, T. Margalith, D. A. Steigerwald, M. O. Holcomb, P. S. Martin, and M. R. Krames, Appl. Phys. Lett. 89, 071109 (2006).

- <sup>5</sup>H. Kim, J. Cho, J. Wook Lee, S. Yoon, H. Kim, C. Sone, and Y. Park, Appl. Phys. Lett. 90, 161110 (2007).

- <sup>6</sup>C. H. Kuo, H. C. Feng, C. W. Kuo, C. M. Chen, L. W. Wu, and G. C. Chi, Appl. Phys. Lett. 90, 142115 (2007).

- <sup>7</sup>D. A. Stocker, E. F. Schubert, and J. M. Redwing, Appl. Phys. Lett. 73, 2654 (1998).

- <sup>8</sup>J. J. Wierer, M. R. Krames, J. E. Epler, N. F. Gardner, M. G. Craford, J. R. Wendt, J. A. Simmons, and M. M. Sigalas, Appl. Phys. Lett. 84, 3885

- <sup>9</sup>M. Kwon, J. Y. Kim, I. K. Park, K. S. Kim, G. Y. Jung, S. J. Park, J. W. Kim, and Y. C. Kim, Appl. Phys. Lett. 92, 251110 (2008).

- <sup>10</sup>J. K. Kim, S. Chhajed, M. F. Schubert, E. F. Schubert, A. J. Fischer, M. H. Crawford, J. Cho, H. Kim, and C. Sone, Adv. Mater. 20, 801

- <sup>11</sup>T. S. Oh, S. H. Kim, T. K. Kim, Y. S. Lee, H. Jeong, G. M. Yang, and, E. K. Suh, Jpn. J. Appl. Phys. 47, 5333 (2008).

- <sup>12</sup>C. F. Lin, Z. J. Yang, B. H. Chin, J. H. Zheng, J. J. Dai, B. C. Shieh, and C. C. Chang, J. Electrochem. Soc. 153, G1020 (2006).